SAN JOSE STATE UNIVERSITY Electrical Engineering Department

# Bottom up IC design-flow Using an Analog Leaf Cell

IC DESIGN GROUP SAN JOSE STATE UNIVERSITY

## A tutorial guide for using CDS tools for IC design in Leaf Cell

Shao Ng Eric Basham David W. Parent Electrical Engineering, SJSU One Washington Square San Jose, CA 95192-0084 Phone 408.924.3963 • Fax 408.924.2925

## **Table of Contents**

| HAPTER I: INTRODUCTION                                                                                                                                                                                                              | 7                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 1. The Leaf Cell:                                                                                                                                                                                                                   |                                              |

| How to size:                                                                                                                                                                                                                        |                                              |

| Initial Design                                                                                                                                                                                                                      |                                              |

| Schematic Capture                                                                                                                                                                                                                   |                                              |

| Pre - Layout                                                                                                                                                                                                                        |                                              |

| Layout                                                                                                                                                                                                                              |                                              |

| Design Rule Checking                                                                                                                                                                                                                |                                              |

| Circuit Extraction                                                                                                                                                                                                                  |                                              |

| Layout versus Schematic                                                                                                                                                                                                             |                                              |

| Post Extraction Simulation                                                                                                                                                                                                          |                                              |

| Fabrication and Test                                                                                                                                                                                                                |                                              |

| Design 1: Current Mirror:                                                                                                                                                                                                           |                                              |

| Design 2: OTA:                                                                                                                                                                                                                      |                                              |

|                                                                                                                                                                                                                                     |                                              |

| HAPTER 2: A CURRENT MIRROR TUTORIAL                                                                                                                                                                                                 |                                              |

| Section 1: Initial Design                                                                                                                                                                                                           |                                              |

| Section 2: Getting started with Schematic Capture and Spice Simulation                                                                                                                                                              |                                              |

| Design entry through schematic capture:                                                                                                                                                                                             |                                              |

| Creating a new library:                                                                                                                                                                                                             |                                              |

| Creating a schematic view:                                                                                                                                                                                                          |                                              |

| Creating a symbol view:                                                                                                                                                                                                             |                                              |

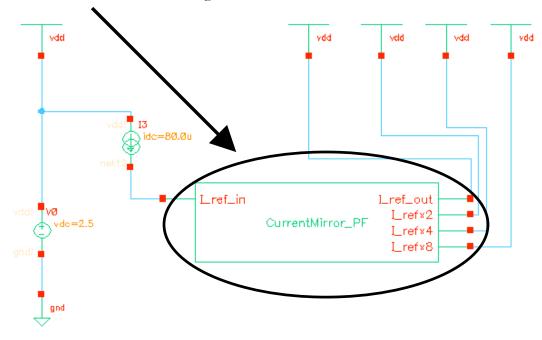

| Creating a test bench:                                                                                                                                                                                                              |                                              |

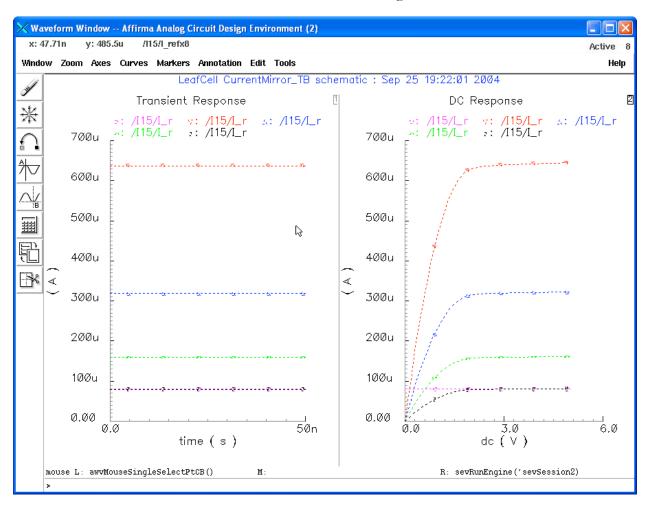

| Simulation in Spectre Spice using the Affirma environment:                                                                                                                                                                          |                                              |

| Section 3: Layout                                                                                                                                                                                                                   |                                              |

| Pre-Layout of the CurrentMirror                                                                                                                                                                                                     |                                              |

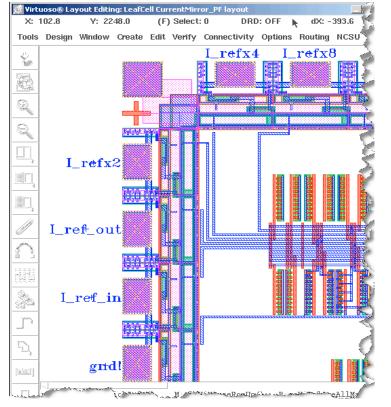

| Layout in Leaf Cell:                                                                                                                                                                                                                |                                              |

|                                                                                                                                                                                                                                     |                                              |

| Design Rule Checking (DRC)                                                                                                                                                                                                          |                                              |

| Design Rule Checking (DRC)<br>Circuit Extraction                                                                                                                                                                                    |                                              |

| Design Rule Checking (DRC)                                                                                                                                                                                                          |                                              |

| Design Rule Checking (DRC)<br>Circuit Extraction                                                                                                                                                                                    |                                              |

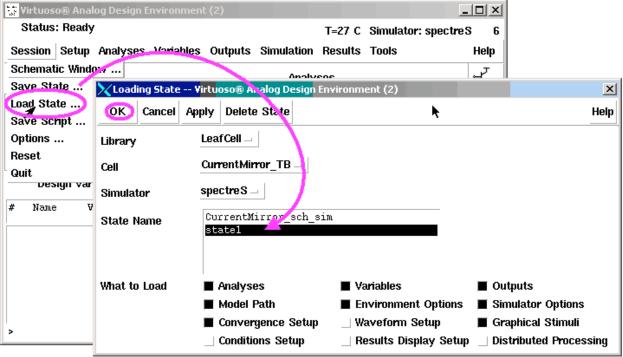

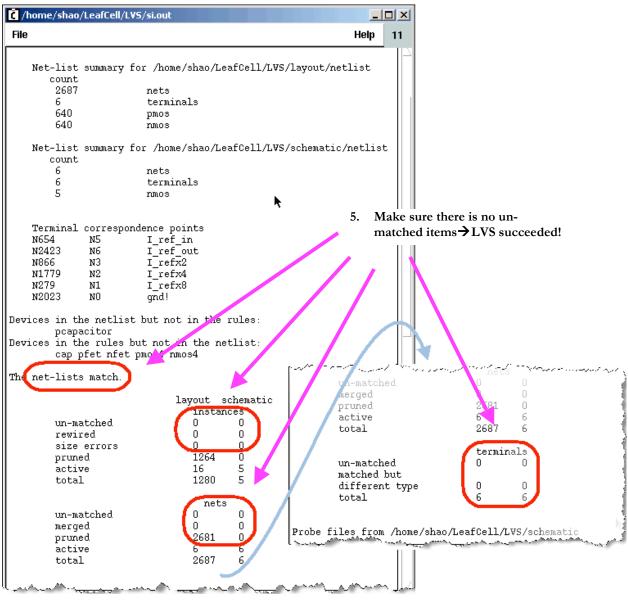

| Design Rule Checking (DRC)<br>Circuit Extraction<br>Layout versus Schematic (LVS)<br>Build Analog Extracted View:<br>Post Extraction Simulation                                                                                     | 58<br>59<br>61<br>64<br>64                   |

| Design Rule Checking (DRC)<br>Circuit Extraction<br>Layout versus Schematic (LVS)<br>Build Analog Extracted View:                                                                                                                   | 58<br>59<br>61<br>64<br>64                   |

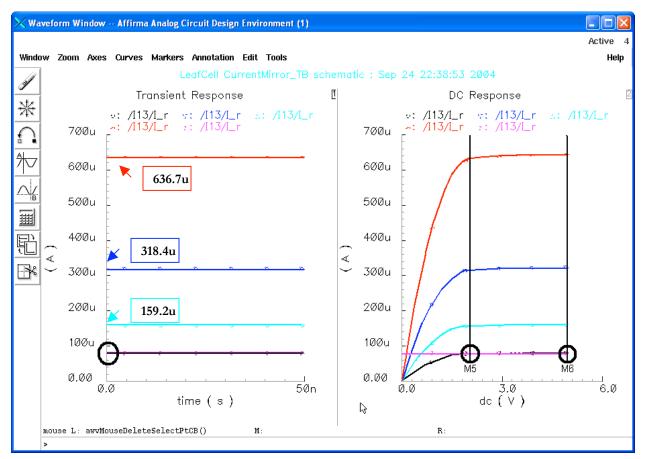

| Design Rule Checking (DRC)<br>Circuit Extraction<br>Layout versus Schematic (LVS)<br>Build Analog Extracted View:<br>Post Extraction Simulation<br>Put in the Pad frame and Extraction Simulation:<br>Simulation for the Slew Rate: | 58<br>59<br>61<br>64<br>65<br>69<br>78       |

| Design Rule Checking (DRC)<br>Circuit Extraction<br>Layout versus Schematic (LVS)<br>Build Analog Extracted View:<br>Post Extraction Simulation<br>Put in the Pad frame and Extraction Simulation:                                  | 55<br>55<br>61<br>64<br>65<br>65<br>65<br>78 |

|                                                                       | .07                                                                                                                                                                            |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ection 1: Initial Design                                              | 87                                                                                                                                                                             |

| ection 2: Getting started with Schematic Capture and Spice Simulation |                                                                                                                                                                                |

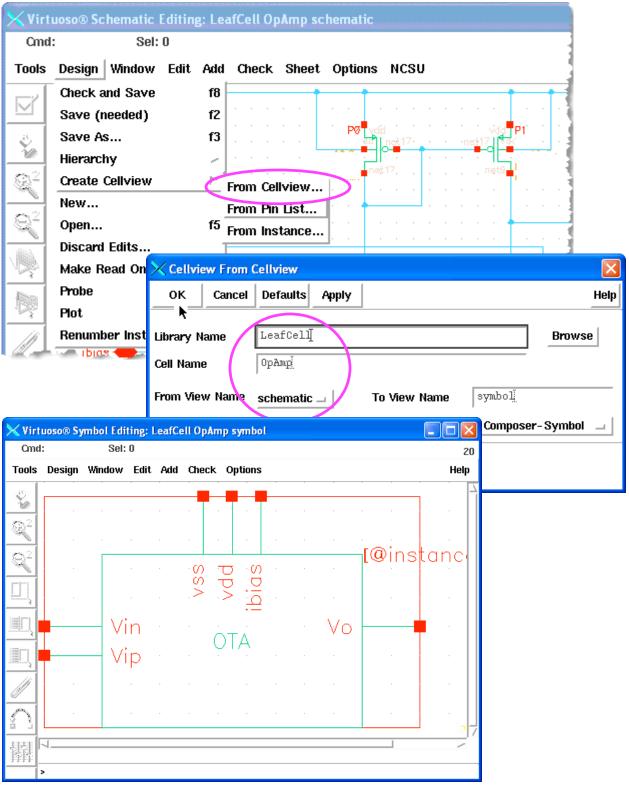

| reating the schematic view:                                           | 89                                                                                                                                                                             |

|                                                                       |                                                                                                                                                                                |

|                                                                       |                                                                                                                                                                                |

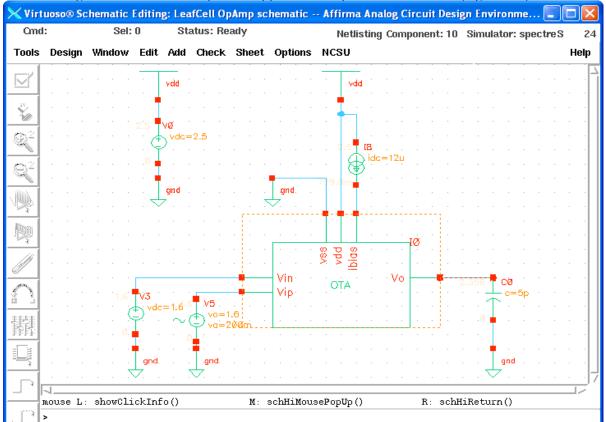

| mulation in Spectre Spice using the Affirma environment:              |                                                                                                                                                                                |

| r                                                                     | ction 1: Initial Design<br>ction 2: Getting started with Schematic Capture and Spice Simulation<br>eating the schematic view:<br>eating a symbol view:<br>eating a test bench: |

#### LIST OF FIGURES:

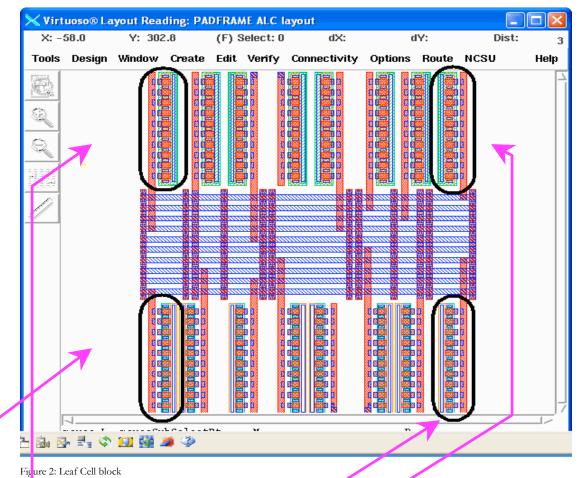

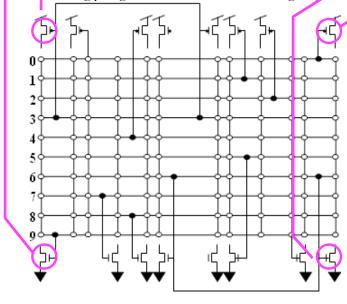

| Figure 1: Leaf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | f Cell in Pad Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

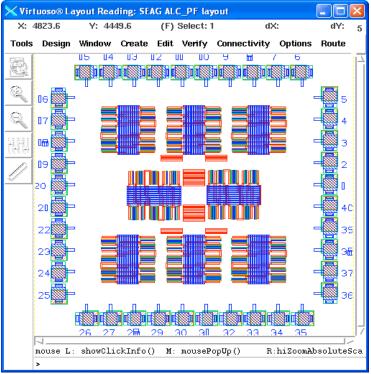

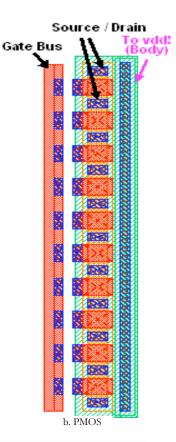

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | f Cell block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

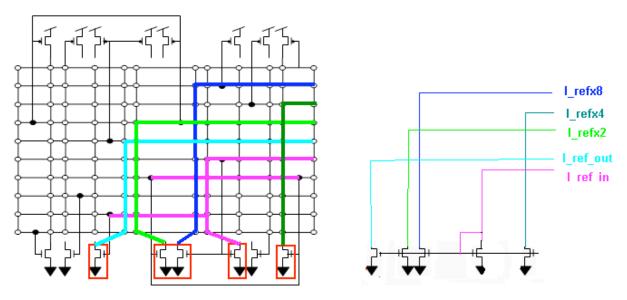

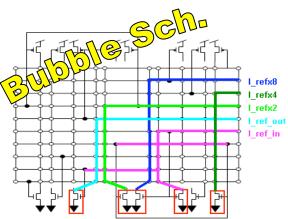

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ble Schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ingle Transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

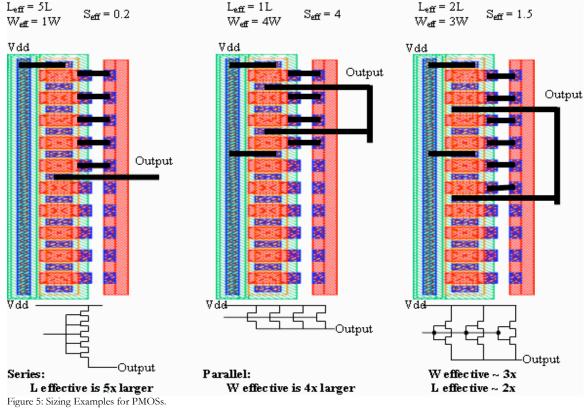

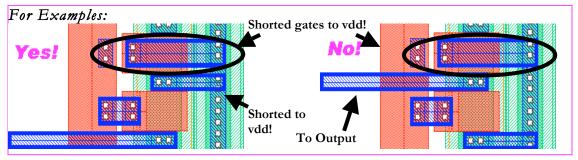

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ng Examples for PMOSs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

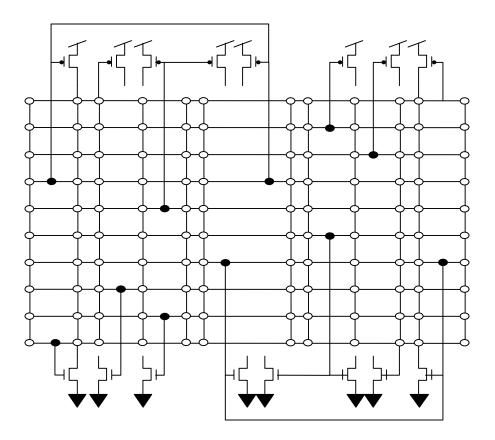

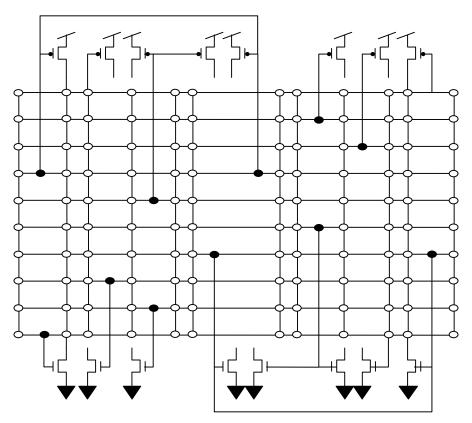

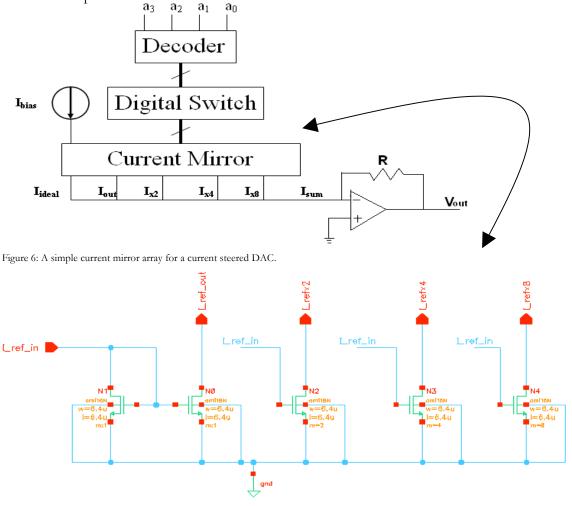

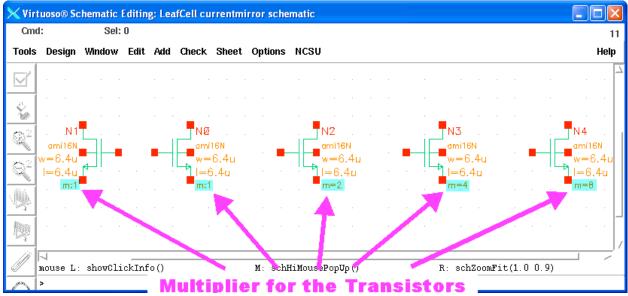

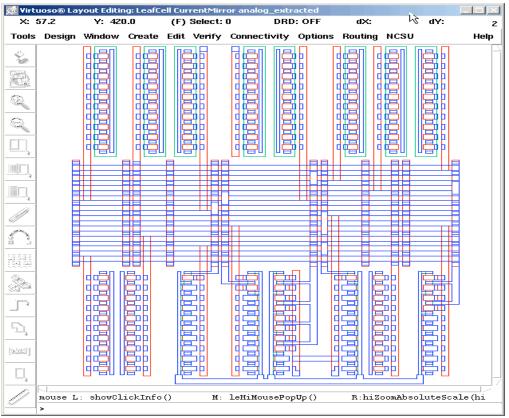

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | mple current mirror array for a current steered DAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

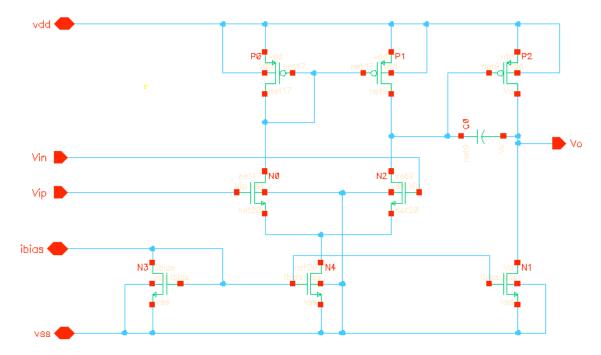

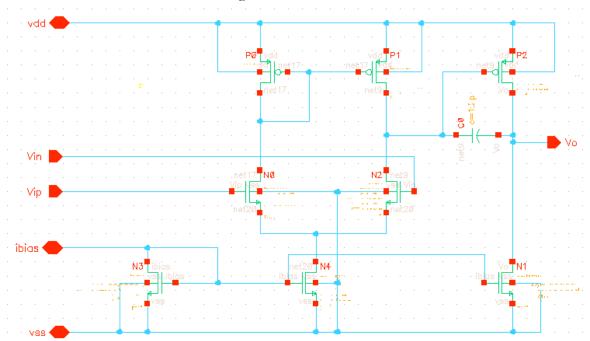

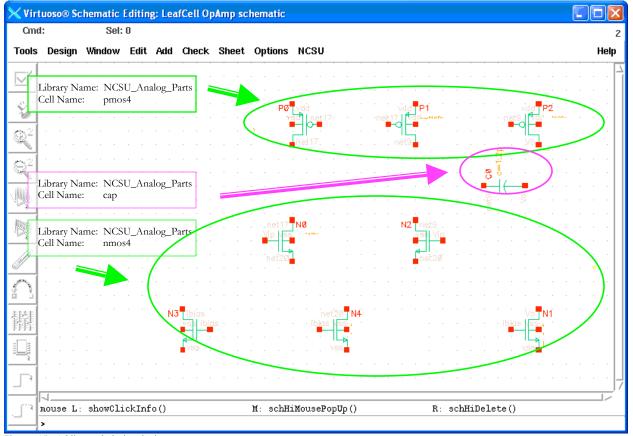

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | mple OTA (Operational Transconductance Amplifier)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 9: Mak                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ing a directory and listing the contents of a directory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | anging your present working directory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | arting CDS tools (icfbIC Front to Back)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 12: Th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | e CIW window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | prary Manager                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 14: W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | here to go for the new project directory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | eating a Library1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | pdated library manager showing LeafCell project directory1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | p-up: Creating a new cell view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 18: Cre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | eating a new schematic view                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | lding an instance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | owsing for components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | oosing the right noncess                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | becifying the nmos needed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 24: Sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | imping down the nmos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

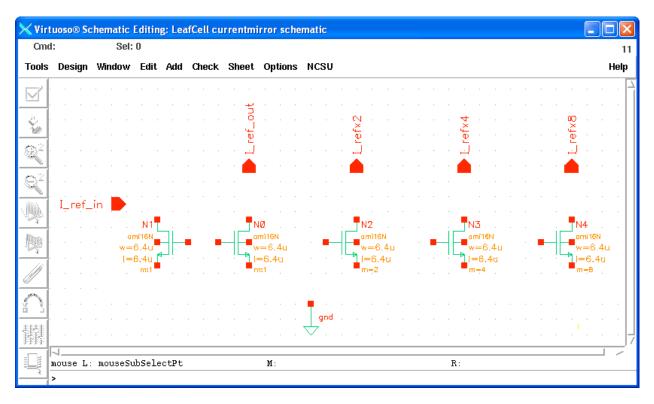

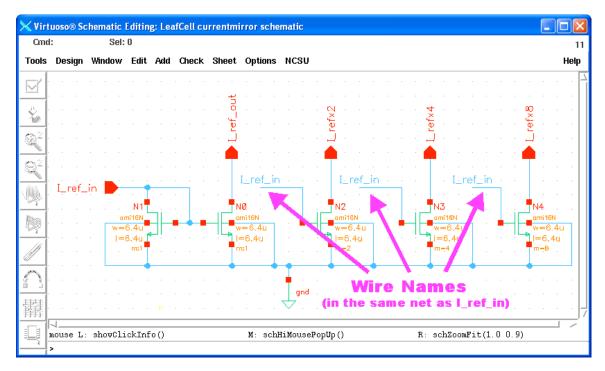

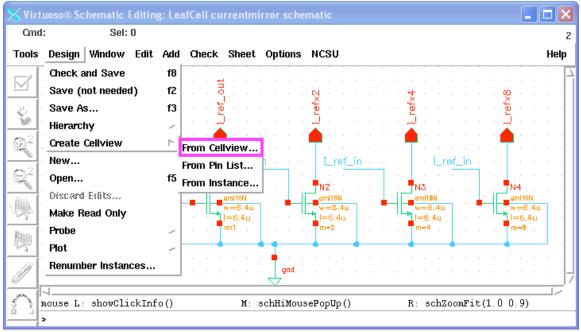

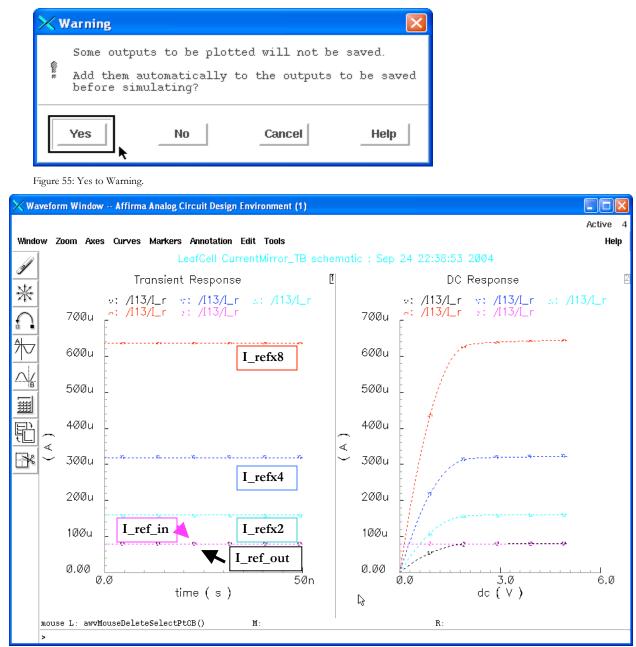

| Figure 25: Pla                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | icing the transistors in schematic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |